# Strategies for End-to-End Timing Guarantees in a Centralized Software Defined Vehicle Architecture Combining CAN With TSN Backbone

CHALLENGES MEET EZE TIMINGS IN SOV UPGRADABLE ARCHITECTURE

SCALABLE GATEWAYING STRATEGIES

EZE & TSN BACKBONE CONFIGURATION

TIME EXPERTS

TIER-1

OEM

COOPERATION

## Agenda

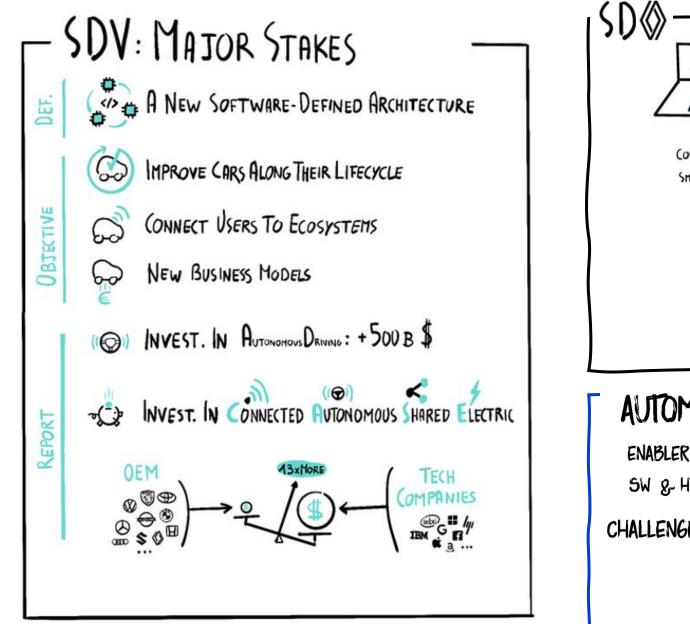

- Renault Perspective on SDV & end to end gatewaying strategies

- RTaW Network Design and Validation Tools

- Bosch plugins in simulation for enhanced optimization

- Takeaways & Future Work

# RENAULT PERSPECTIVE ON SDV & END TO END GATEWAYING STRATEGIES

JOSETXO VILLANUEVA / IN-VEHICLE NETWORK EXPERT @ RENAULT BOUCHRA ACHEMLAL / ETHERNET+TSN SPECIALIST @ RENAULT

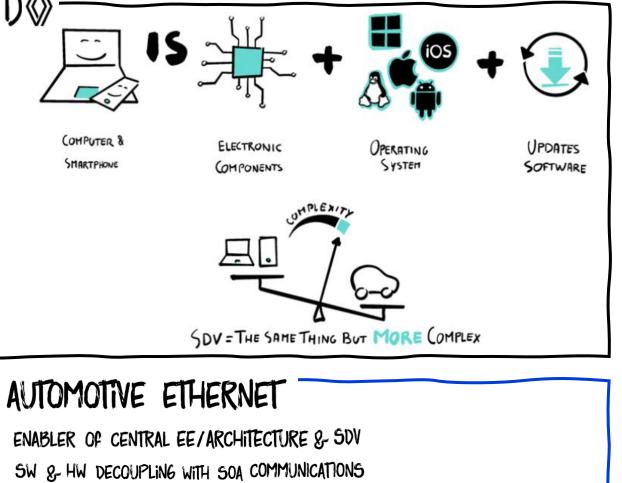

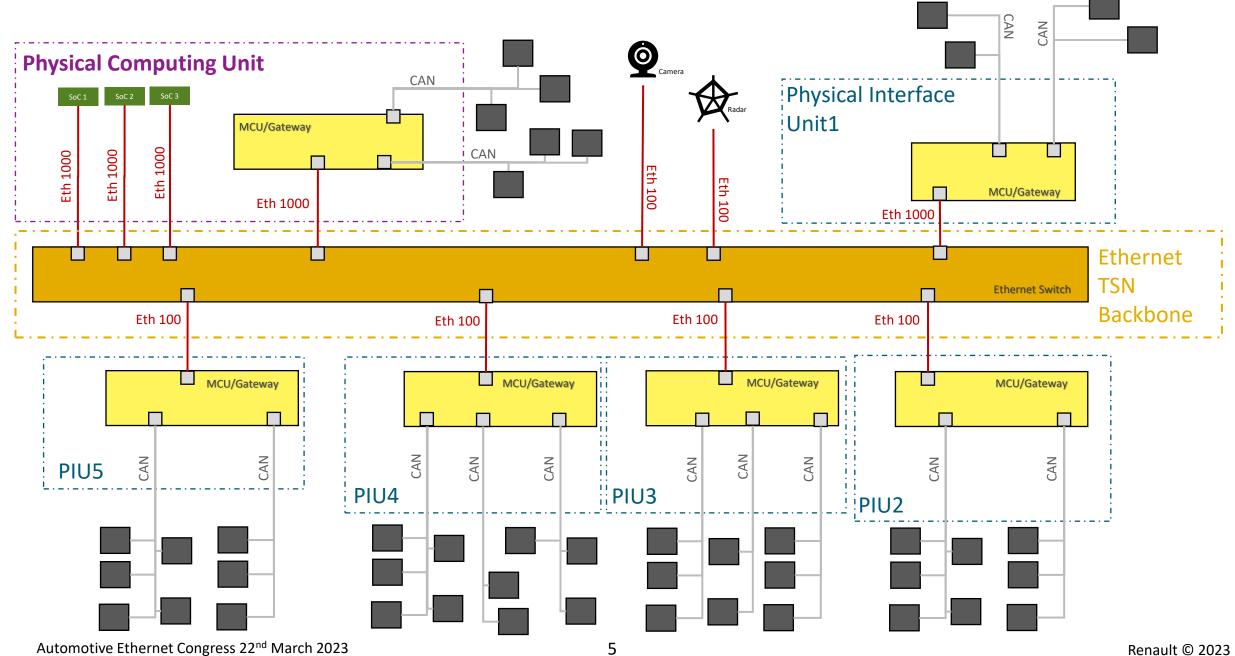

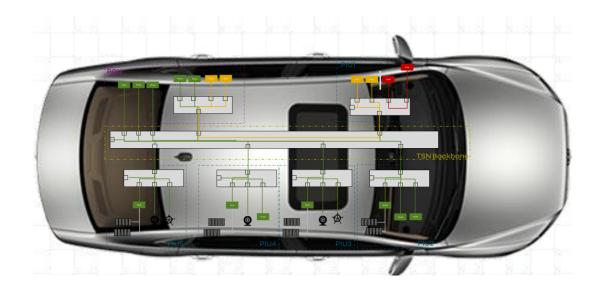

## **EE ARCHITECTURE : Topology**

## **EE Architecture : Constraints & Strategies**

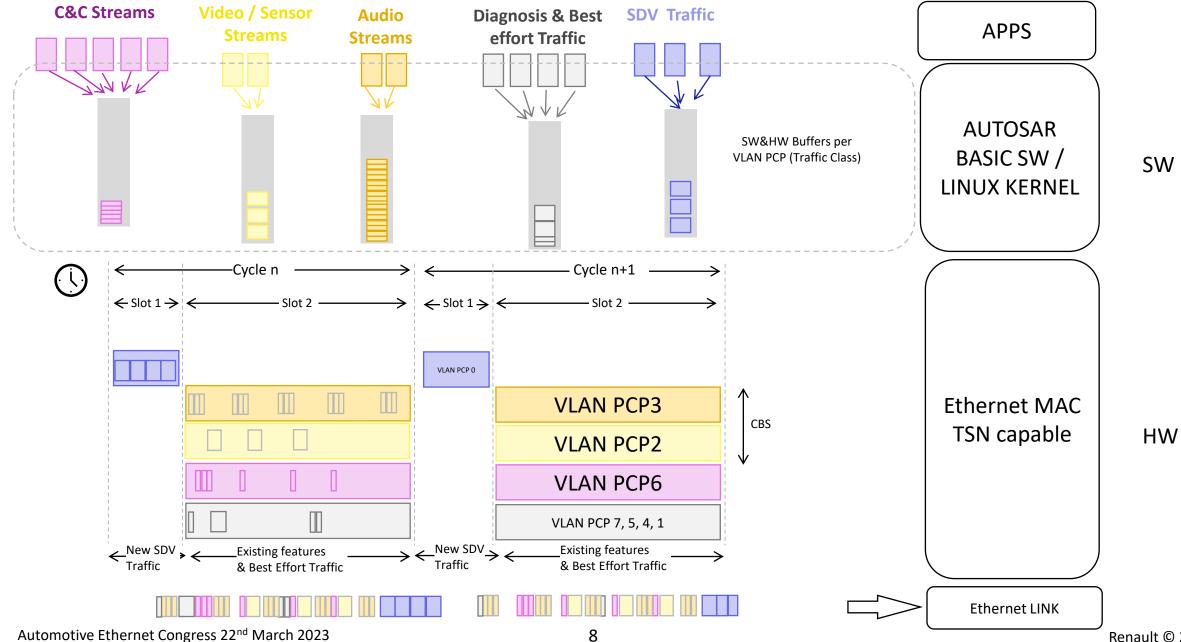

#### **Mixed critical traffic**

- Command & Control (Steering, Safety, Time-Constrained)

- Sensor & Video Traffic (Bursty data, ADAS, data fusion)

- Audio streams (Time sensitive, QoS, AR)

- Diagnosis & Best Effort

- SDV Scalable Traffic (Future Features, OTA)

## Strategy

- → Control the CAN<->Ethernet Gatewaying

- $\rightarrow$  Deploy an appropriate TSN configuration

Switch Buffer depth = f(BW, #ports, TSN config)

Gateways Buffer depth=f(CPU load, Latency )

Avoid Packet Loss (Monitoring buffer usage)

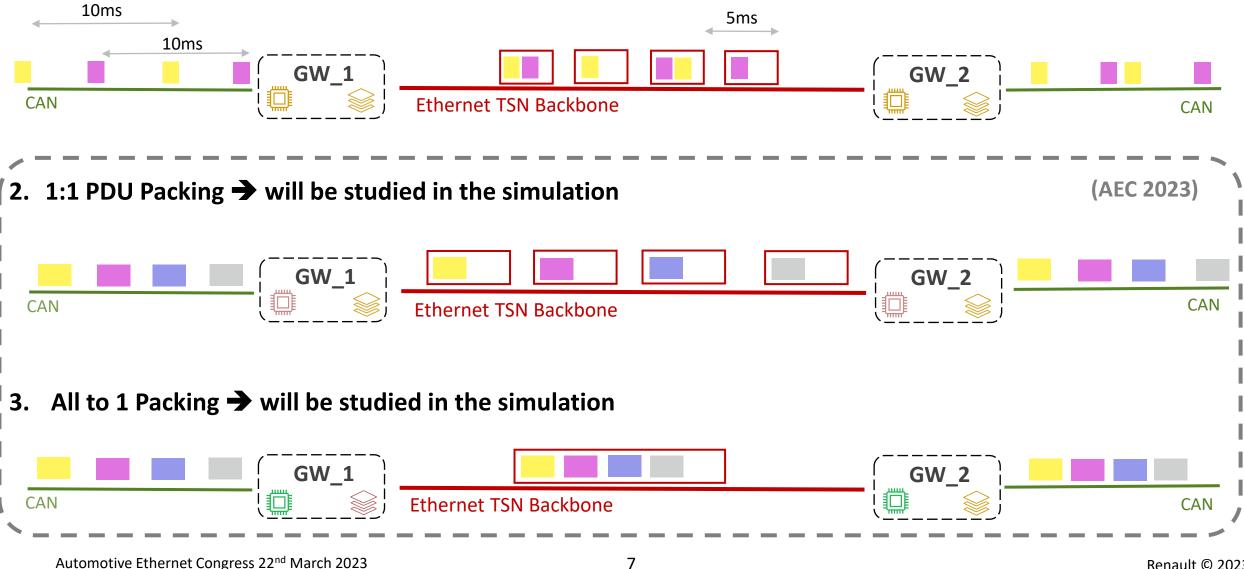

## E2E CAN<->Ethernet Gatewaying Strategies

**Command & Control traffic**

1. Snapshot Strategy (PDU ½ period packing) - Was simulated in a previous study (EIPATD 2019)

**Buffer Depth**

CPU Load

## **TSN DEPLOYMENT Strategy**

# **Network Design and Validation Tools**

Jörn Migge, CTO RealTime-at-Work

Automotive Ethernet Congress 22nd March 2023

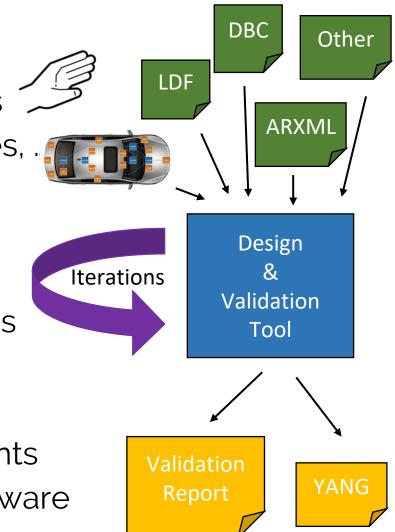

# Working with the tool

Input: which information is needed?

- Topology: link speeds, switching delays, connections

- Frames, PDUs, Services: periods, payloads, burst sizes, .

**Design & Validation**

- Optimal configuration of TSN mechanism

- Validation of constraints through simulation & analysis

## Output

- Validation report on latency and throughput constraints

- TSN scheduling parameters in YANG format for hardware

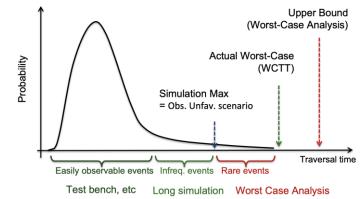

# Roles of Worst-Case Analysis and Simulation

- Worst-Case Analysis: computed upper bounds

- Validation of (hard) latency and memory constraints

- Simulation: statistics

- Validation of (soft) latency, memory and throughput constraints

- Illustration through Gantt charts

- Refined modelling through simulator plugins: gateways

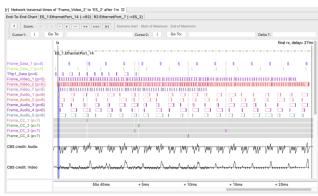

#### Screenshots from RTaW-Pegase

#### Frame Delay Distribution

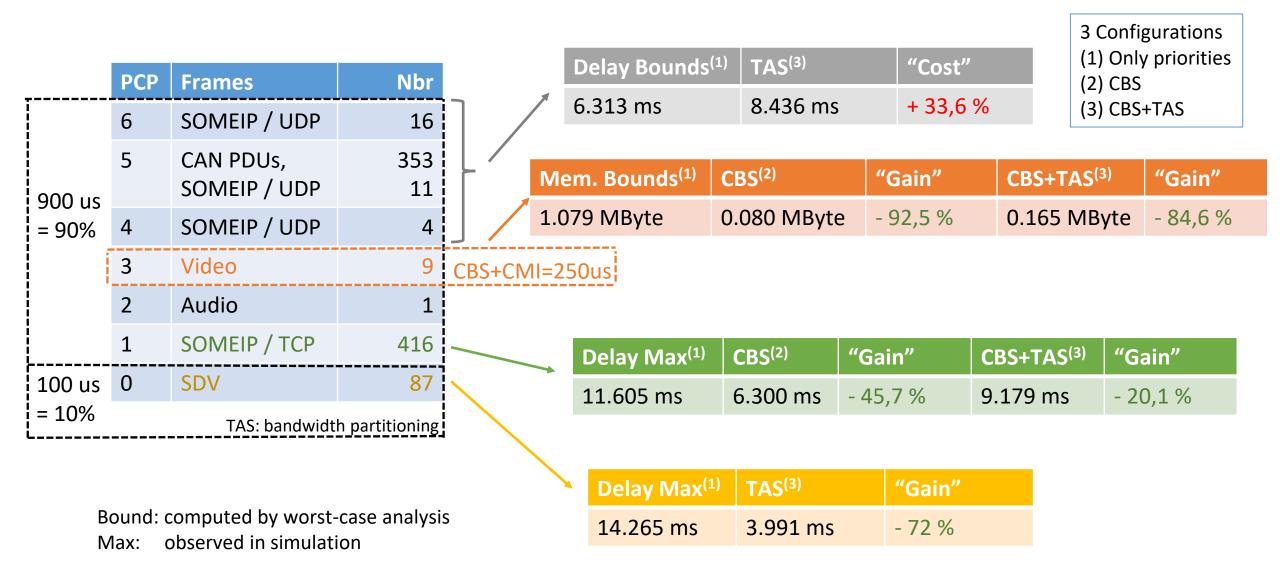

# CBS + CMI – video stream shaping

## Motivation

- Shaping of bursty traffic (generally) *reduces memory* requirements and *increases throughput* of lower priority traffic.

## Difficulties

- Shaping means *delaying* the shaped frames, but their *latency constraints* must still be met!

- Not only shaping inside the network is useful but also at the *entrance of the network* (CMI, TSpec).

## Solution

- CBS *configuration algorithm* based on *Worst-Case Analysis* to guarantee latency constraints.

# TAS – for bandwidth partitioning

### Motivation

- Some *not well known or uncontrolled traffic* whose interference can be blocked through *bandwidth partitioning* with TAS.

Design choices

- Size of the slots for the two kinds of traffics => period of the gate control list.

Difficulties

- Latency constraints, not only of the shaped video stream must be met.

- *CBS* configuration must be adapted to the presence of *TAS* slots. **Solution**

- CBS *configuration algorithm* based on *Worst-Case Analysis* able to cope with TAS + CBS.

# Impact of CBS/CMI and TAS

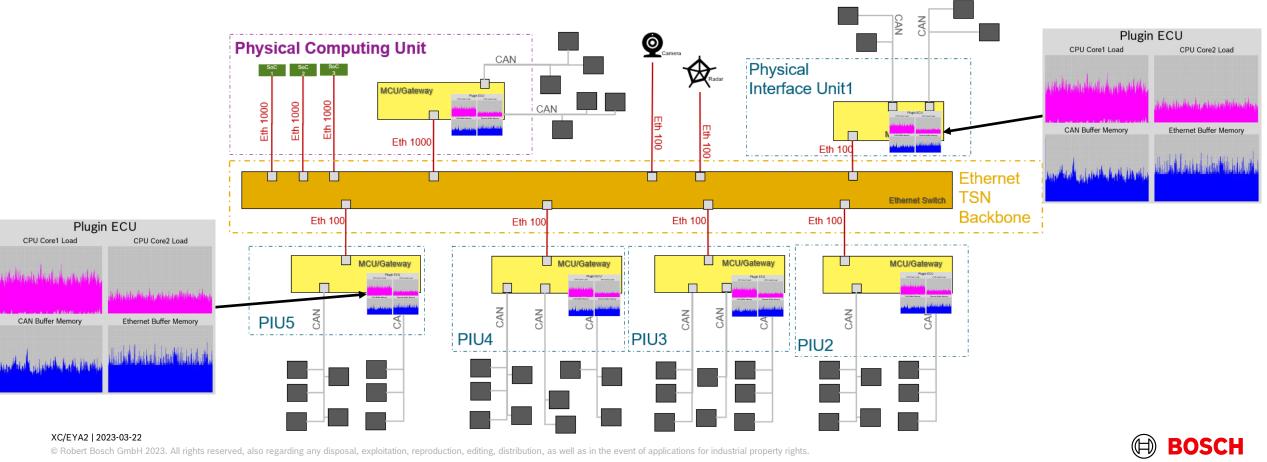

# Plugins in simulation for enhanced optimization

Damon Martini Robert Bosch GmbH Communications Simulation Expert

## What is a plugin?

- Simply put a java model (or models) integrated into the RTaW Pegase simulation environment

- This plugin model can describe anything useful for network communications simulation:

- Physical layer delays

- Gateways (Autosar, other)

- Ethernet switches

## Why use plugins?

- ECU frame processing time is becoming a dominant factor in end to end latency compared to frame time on the wire

- Therefore it's VITAL that these performance characteristics are included in the architecture modelling

- Also if we know the CPU load and input buffer memory we can better engineer the right microcontroller for the job

#### XC/EYA2 | 2023-03-22

© Robert Bosch GmbH 2023. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

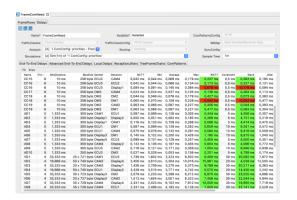

## Plugins in the study context

- Detailed modelling of Zone ECUs and Vehicle Computers

- Used for ECU optimization when packing/unpacking CAN PDUs transported over Ethernet

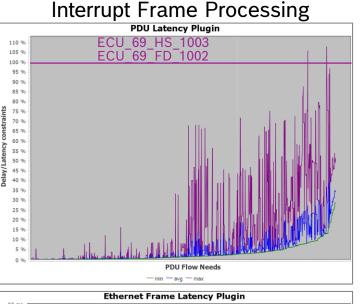

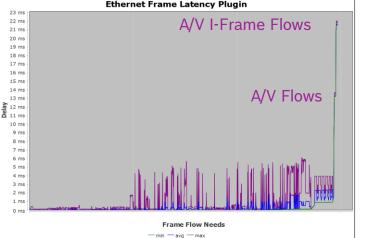

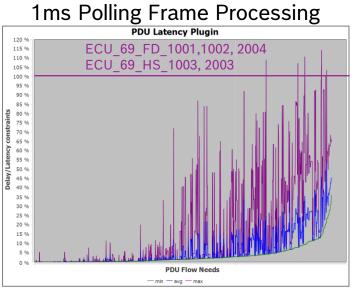

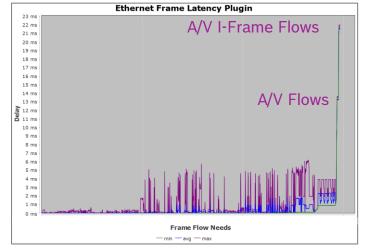

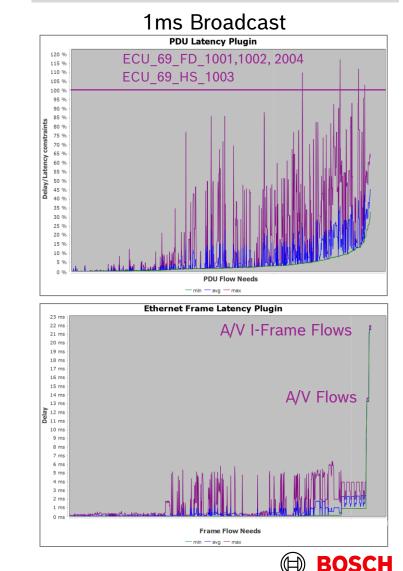

## **Results: PDU Latency & Ethernet Frame Latency**

#### 1:1 PDU Packing

#### All to 1 Packing

#### XC/EYA2 | 2023-03-22

© Robert Bosch GmbH 2023. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

#### Automotive Ethernet Congress 22<sup>nd</sup> March 2023

18

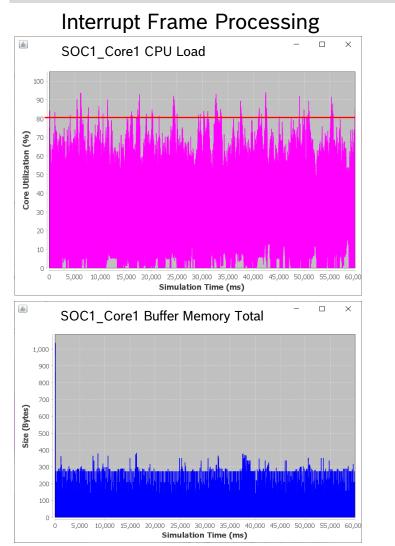

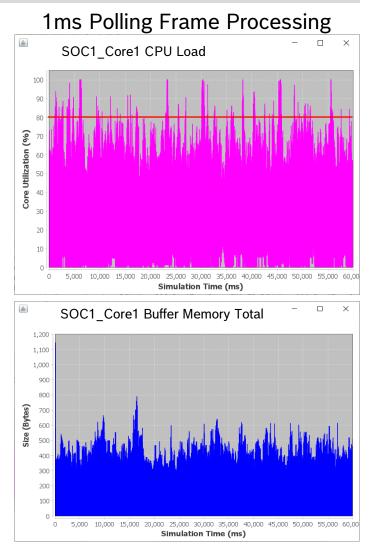

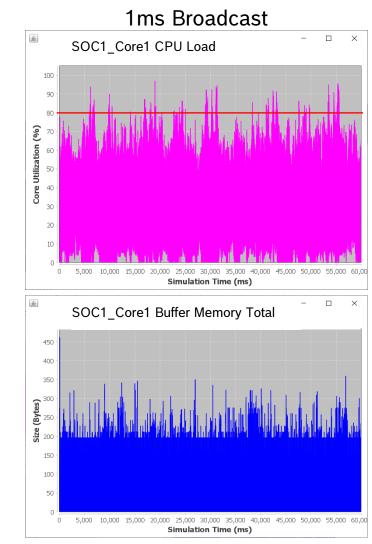

## Results: CPU Load & Memory

#### 1:1 PDU Packing

#### BOSCH

#### XC/EYA2 | 2023-03-22

© Robert Bosch GmbH 2023. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

#### Automotive Ethernet Congress 22<sup>nd</sup> March 2023

19

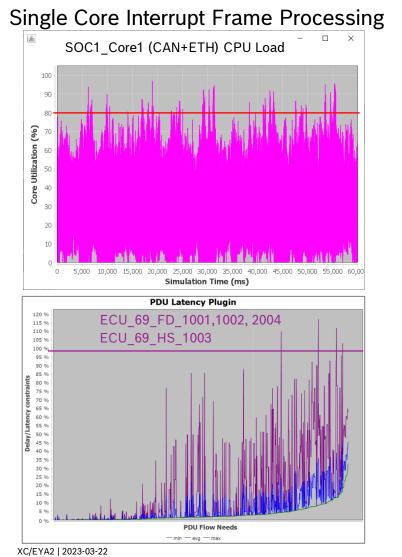

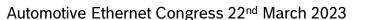

## Results: CPU Load Single vs Dual Core

#### Max allowed CPU load

— min — avg — max

#### All to 1 Packing

Core

© Robert Bosch GmbH 2023. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

### BOSCH

20

15 %

10 %

5 %

0 %

PDU Flow Needs

- min - avg - max

## **Simulation Based Results**

|                                                                                                                                                                                                                                |                                                                              | KPI Analysis                            |                                       |             |               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------|-------------|---------------|

|                                                                                                                                                                                                                                |                                                                              | PDU End to<br>End Latency               | Max Ethernet<br>Link Loads<br>(Top 3) | CPU<br>Load | CPU<br>Memory |

| Optimization Step                                                                                                                                                                                                              | 1:1 Unicast<br>(All processed by interrupt)                                  | 14 <b>76</b> from total<br>of 1478 pass | 47.96%<br>13.63%<br>12.50%            | ×           | Nº 2          |

|                                                                                                                                                                                                                                | 1:1 Unicast<br>(All processed by 1ms task)                                   | 14 <b>72</b> from total<br>of 1478 pass | 47.99%<br>13.63%<br>12.51%            | ×           | Nº 3          |

|                                                                                                                                                                                                                                | Many-1 Broadcast 1ms transmission<br>(All processed by SingleCore interrupt) | 14 <b>74</b> from total<br>of 1478 pass | 48.99%<br>21.58%<br>13.56%            | ×           | Nº 1          |

|                                                                                                                                                                                                                                | Many-1 Broadcast 1ms transmission<br>(All processed by DualCore interrupt)   | 14 <b>75</b> from total<br>of 1478 pass | 48.91%<br>21.59%<br>13.56%            |             | Nº 1          |

| XC/EYA2   2023-03-22<br>© Robert Bosch GmbH 2023. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights. |                                                                              |                                         |                                       |             | BOSCH         |

21

## **Takeaways & Future Work**

# SDV Takeaways

CBS, Multicore gateways

TAS, Monocore gateways

- TSN strategy needs to be carefully considered to ensure the Ethernet switch resources don't become the bottleneck

- Using TAS for scalability comes at a cost (2x buffer overconsumption)

- CBS is effective in reducing Ethernet port memory usage and lower priority traffic latency

- To meet deadlines, CAN2ETH gatewaying latency needs to be < 1ms

- Gatewaying strategy simulated doesn't impact link load or PDU latency – Services/Audio/Video are the main contributors

- Putting CAN/Ethernet frame processing tasks on different cores achieves CPU load requirement

# **Future Work**

Testbeds vs simulations Qcr, PLCA, Multigig GTW optimizations

- Correlating Ethernet switch buffer values and latency values from simulation with real implementation

- Exploring possible Ethernet backbone upgrades to ensure future scalability (eg: 10BASE-T1S, multi-Gb links)

- Simulating other scheduling mechanisms (eg: Qcr, PLCA)

- Gateway plugin optimization modeling

- CPU loads via communication interface-CPU core mapping

- use of Complex Device Drivers, hardware acceleration, IEEE 1722 Transport Protocol

# Thank you

# **Questions**?

Josetxo VILLANUEVA In-vehicle Network expert JOSE.VILLANUEVA@RENAULT.COM

Bouchra ACHEMLAL Ethernet/TSN Specialist BOUCHRA.ACHEMLAL@RENAULT.COM

Damon Martini

XC/EYA2 Cross-Domain Computing Solutions

damon.martini2@de.bosch.com

Contact: jorn.migge@realtimeatwork.com C.T.O. RTaW